Run the Check Syntax process (under Synthesize) to make sure your code is entered correctly, and save your design. You can use your own code, or copy the solution below: This tutorial will use a full adder that is the same as the one you created in Lab 0. If you accidentally select a simulator other than ISE Simulator for your project, or if you open a previous project that had a different simulator selected, you can change the simulator by right-clicking on xc2vp30-7ff896 in the Sources window in ISE and selecting Properties. Once you've entered them, click Next and Finish until your module is generated. The inputs and outputs for the module are shown below. Set the properties as shown below, making sure toĬlick Next, and create a new Verilog Module source named full_adder. AfterĮntering a project name and location, you'll be prompted for the

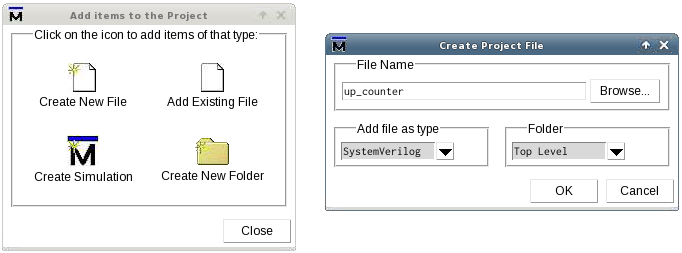

Simulate with testbenchAdd signal to waveform27Ĥ.Open the ISE Project Navigator and create a new project. Simulate with testbenchAdd signal to waveform26Ĥ. Simulate with testbenchSelect Simulate > Start simulationĤ. Simulate with testbenchAfter completed coding, select Compile > Compile all24Ĥ. Simulate with testbenchCreate testbench file to project23Ĥ. To stop simulation, slect Simulate > End simulationĬontents4.Simulate with testbench3.Simulate without testbench2.Design Project1.Introduction22Ĥ. Simulate without testbench20SimulateSelect Run all Simulate without testbench19With output signalģ. Simulate without testbench18Waveform windowģ. Simulate without testbench17Waveform windowģ. Simulate without testbench16Modify waveforms for SimulationRight clickģ. Simulate without testbench15Create waveforms for Simulationģ. Simulate without testbenchSelect Simulate > Start simulation, Start Simulation window will appearģ. Design ProjectAfter completed coding, select Compile > Compile allġ1Contents4.Simulate with testbench3.Simulate without testbench2.Design Project1.Introduction12ģ. Design ProjectA Create Project pop-up box will appearġ.Enter the name of the projectChoose Project Locationġ02. In the displayed window select File > New > ProjectĦ2. Design ProjectOpen the ModelSim simulator. Design ProjectSimple example : f(x1, x2, x3) = x1x2 + x2x3 + x3x1ĥ2. IntroductionModelSim is a verification and simulation tool for VHDL, Verilog, SystemVerilog, and mixed-language designs.Software : ModelSim-Altera 6.6d Starter EditionReferences : Introduction to Simulation of Verilog Designs Using ModelSim Graphical Waveform Editor (Altera).ModelSim Tutorial (Mentor Graphics).Ĭontents4.Simulate with testbench3.Simulate without testbench2.Design Project1.Introduction4Ģ. Introduction to Simulation of Verilog Designsusing ModelSim-AlteraPresenter: Phong BuiEmail: Image Processing GroupIC Design LabHanoi LOGOġContents4.

0 kommentar(er)

0 kommentar(er)